## **PRELIMINARY**

## BIT MAP LCD DRIVER

## **■ GENERAL DESCRIPTION**

The NJU6572A is a bit map LCD driver to display graphics or characters

It contains 2,560 bit display data RAM, microprocessor interface circuits, instruction decoder, and 16-common and 61-segment drivers

The bit image display data sent from 8- or 16-bit MPU are stored in the display data RAM and drives Dot Matrix LCD Panel by the common and segment drivers.

The 16-common and 61-segment drivers can drive graphics or 12-character 2-line with icon data.

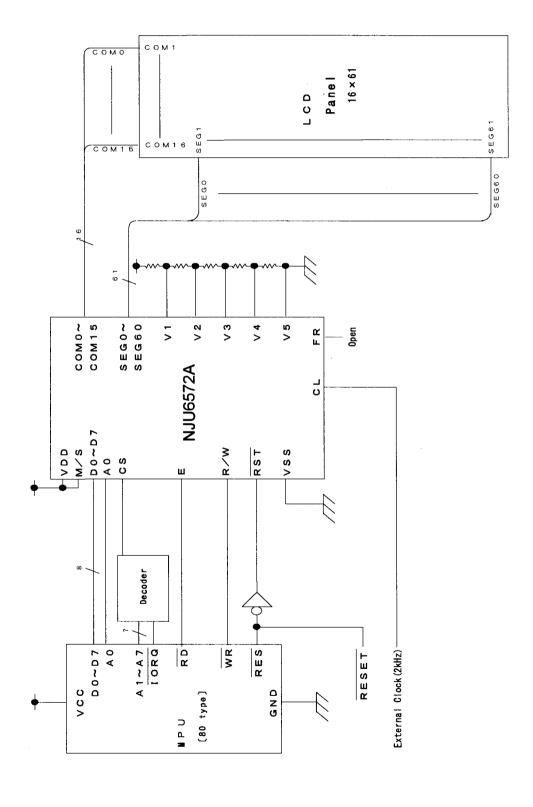

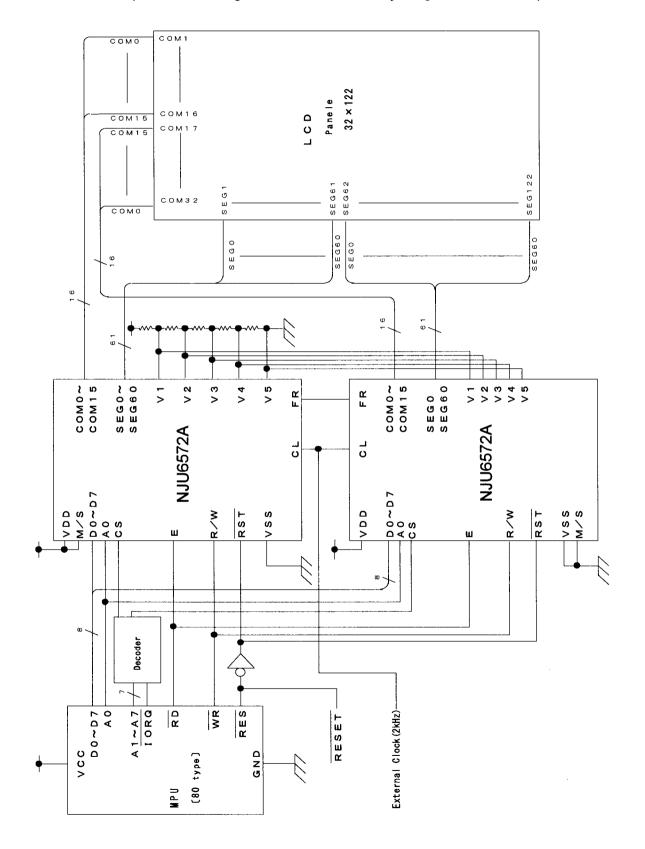

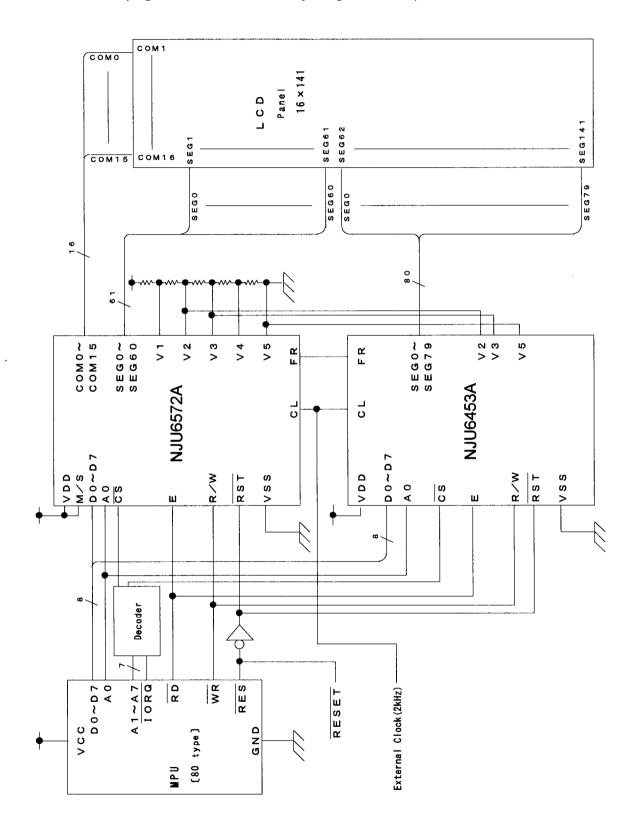

The NJU6572A can combine with the NJU6572A or 6453A to expand the display capacity to 32 x 122 dots or 16 x 141 dots of graphics or character display by using the extension function of NJU6572A. Furthermore, low current consumption due to the external clock input and wide operating voltage are useful apply to the small sized battery operated items.

#### **■ PACKAGE OUTLINE**

NJU6572AC

## **■ FEATURES**

- Direct Correspondence between Display Data RAM and LCD Pixel

- Display Data RAM 2,560 bits 80 x 8 x 4

- Direct Interface with 8- or 16-bit MPU

(Both of 68 and 80 type MPU can connect directly)

- Extension Function (can combine with NJU6572A or 6453A)

- Read Out From the Display Data RAM

- 16-common and 61-segment Drivers

- Programmable Duty Ratio ; 1/16 or 1/32 Duty

- Useful Instruction Set

Display Data Read/Write, Display ON/OFF Cont, Display Data RAM Address Set, Status Read, Display Starting Line Set, Static Drive ON/OFF, Duty Ratio Setting, and Read Modify Write,

- Low Power Consumption

- External Clock Input (2kHz)

- Operating Voltage --- 2.4V 5.5V

- LCD Driving Voltage --- 10.0V

- Package Outline --- Chip

- C-MOS Technology

## **■ BLOCK DIAGRAM**

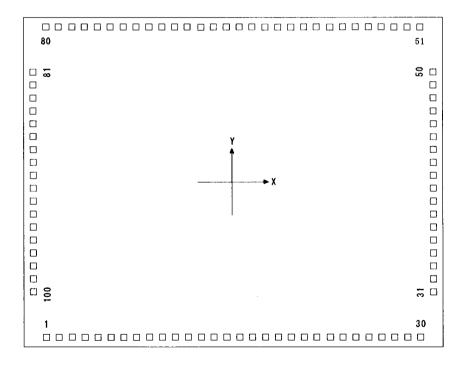

## **PAD LOCATION**

Chip Cente Chip Size X=0um, Y=0um X=4.37mm, Y=3.25mm

Chip Thickness Pad Size 400um ± 30um 100.8um × 100.8um

Pad Pitch

140um

■ PAD COORDIATES

Chip Size 4.37mm x 3.25mm(Chip Center X=0um, Y=0um)

| PAD CO  | ORDIATES       |        |                |

|---------|----------------|--------|----------------|

| PAD No. | Terminal       | X=(um) | Y=(um)         |

| 1       | COM5           | -2031  | -1471          |

| 2       | СОМ6           | -1891  | -1471          |

| 3       | COM7           | -1751  | -1471          |

| 4       | COM8           | -1611  | -1471          |

| 5       | СОМ9           | -1471  | -1471          |

| 6       | COM10          | -1331  | -1471          |

| 7       | COM11          | -1191  | -1471          |

| 8       | COM12          | -1051  | -1471          |

| 9       | COM13          | -911   | -1471          |

| 10      | COM14          | -771   | -1471          |

| 11      | COM15          | -631   | -1471          |

| 12      | SEG60          | -491   | -1471          |

| 13      | SEG59          | -351   | -1471          |

| 14      | SEG58          | -211   | -1471          |

| 15      | SEG57          | -71    | -1471          |

| 16      | SEG56          | 70     | -1471          |

| 17      | SEG55          | 210    | -1471          |

| 18      | SEG53          | 350    | -1471          |

| 19      | SEG53          | 490    | -1471          |

| 20      | SEG52          | 630    | -1471          |

| 21      | SEG52<br>SEG51 | 770    | -1471          |

| 22      | SEG51          | 910    | -1471          |

| <b></b> | SEG30<br>SEG49 | 1050   | -1471          |

| 23      | <del></del>    | 1190   |                |

| 25      | SEG48          | 1330   | -1471<br>-1471 |

|         | SEG47<br>SEG46 | 1470   | -1471<br>-1471 |

| 26      |                |        | -1471          |

| 27      | SEG45          | 1610   |                |

| 28      | SEG44          | 1750   | -1471          |

| 29      | SEG43          | 1890   | -1471          |

| 30      | SEG42          | 2030   | -1471          |

| 31      | SEG41<br>SEG40 | 2030   | -1331          |

| 32      |                | 2030   | -1191          |

| 33      | SEG39          | 2030   | -1051          |

| 34      | SEG38          | 2030   | -911<br>-774   |

| 35      | SEG37          | 2030   | -771           |

| 36      | SEG36          | 2030   | -631<br>404    |

| 37      | SEG35          | 2030   | -491<br>254    |

| 38      | SEG34          | 2030   | -351           |

| 39      | SEG33          | 2030   | -211           |

| 40      | SEG32          | 2030   | -71            |

| 41      | SEG31          | 2030   | 70             |

| 42      | SEG30          | 2030   | 210            |

| 43      | SEG29          | 2030   | 350            |

| 44      | SEG28          | 2030   | 490            |

| 45      | SEG27          | 2030   | 630            |

| 46      | SEG26          | 2030   | 770            |

| 47      | SEG25          | 2030   | 910            |

| 48      | SEG24          | 2030   | 1050           |

| 49      | SEG23          | 2030   | 1190           |

| 50      | SEG22          | 2030   | 1330           |

| PAD No. | Terminal | X=(um) | Y=(um) |

|---------|----------|--------|--------|

| 51      | SEG21    | 2030   | 1470   |

| 52      | SEG20    | 1890   | 1470   |

| 53      | SEG19    | 1750   | 1470   |

| 54      | SEG18    | 1610   | 1470   |

| 55      | SEG17    | 1470   | 1470   |

| 56      | SEG16    | 1330   | 1470   |

| 57      | SEG15    | 1190   | 1470   |

| 58      | SEG14    | 1050   | 1470   |

| 59      | SEG13    | 910    | 1470   |

| 60      | SEG12    | 770    | 1470   |

| 61      | SEG11    | 630    | 1470   |

| 62      | SEG10    | 490    | 1470   |

| 63      | SEG9     | 350    | 1470   |

| 64      | SEG8     | 210    | 1470   |

| 65      | SEG7     | 70     | 1470   |

| 66      | SEG6     | -71    | 1470   |

| 67      | SEG5     | -211   | 1470   |

| 68      | SEG4     | -351   | 1470   |

| 69      | SEG3     | -491   | 1470   |

| 70      | SEG2     | -631   | 1470   |

| 71      | SEG1     | -771   | 1470   |

| 72      | SEG0     | -911   | 1470   |

| 73      | A0       | -1051  | 1470   |

| 74      | cs       | -1191  | 1470   |

| 75      | CL       | -1331  | 1470   |

| 76      | E(RD)    | -1471  | 1470   |

| 77      | R/W(WR)  | -1611  | 1470   |

| 78      | vss      | -1751  | 1470   |

| 79      | DB0      | -1891  | 1470   |

| 80      | DB1      | -2031  | 1470   |

| 81      | DB2      | -2031  | 1330   |

| 82      | DB3      | -2031  | 1190   |

| 83      | DB4      | -2031  | 1050   |

| 84      | DB5      | -2031  | 910    |

| 85      | DB6      | -2031  | 770    |

| 86      | DB7      | -2031  | 630    |

| 87      | VDD      | -2031  | 490    |

| 88      | RST      | -2031  | 350    |

| 89      | FR       | -2031  | 210    |

| 90      | V5       | -2031  | 70     |

| 91      | V3       | -2031  | -71    |

| 92      | V2       | -2031  | -211   |

| 93      | M/S      | -2031  | -351   |

| 94      | V4       | -2031  | -491   |

| 95      | V1       | -2031  | -631   |

| 96      | СОМ0     | -2031  | -771   |

| 97      | COM1     | -2031  | -911   |

| 98      | COM2     | -2031  | -1051  |

| 99      | сомз     | -2031  | -1191  |

| 100     | COM4     | -2031  | -1331  |

|         |          |        |        |

## **■** Terminal Description

| No.                  | Symbol                      | Function                                                                                                                                                                                                 |

|----------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 87                   | <b>V</b> <sub>DD</sub>      | Power Supply : V <sub>DD</sub> =+5V                                                                                                                                                                      |

| 78                   | Vss                         | GND : Vss= 0V                                                                                                                                                                                            |

| 95, 92<br>91, 94, 90 | V1, V2<br>V3, V4, V5        | LCD Driving Voltage Supplying Terminal. Following relation must be maintained.<br>Voo≧V₁≧V₂≧V₃≧V₄≧V₅                                                                                                     |

| 74                   | CS                          | Chip Select Signal Input Terminal. Normally input the decoded signal of Address Bus<br>Signal. Active "L".                                                                                               |

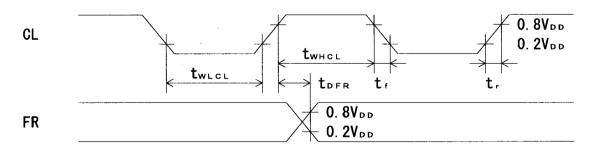

| 75                   | CL                          | Display Data Latch Signal Input Terminal. The Line Counter also count up by this signal rising timing. The synchronized signal of the NJU6470 is required.                                               |

| 76                   | Е                           | <when 68="" connect="" mpu="" the="" to="" type=""> Connect to Enable Clock Input Terminal of 68 type MPU. Active "H".</when>                                                                            |

|                      | (RD)                        | \(\text{When connect to the 80 type MPU}\) Connect to \(\overline{RD}\) Signal Input Terminal of 80 type MPU. Active "L" During this terminal is "L", the Data Bus is output state.                      |

| 77                   | R/W<br>                     | <pre></pre>                                                                                                                                                                                              |

|                      | (WR)                        | When connect to the 80 type MPU> Connect to WR Signal connecting terminal of 80 type MPU. Active "L". The data on the Data Bus is fetch at the rising edge of this signal.                               |

| 73                   | AO                          | Connect to the Address Bus of MPU. The data on the Do~D7 is distinguished between Display Data and Instruction by this signal.  AO H L Data Display Data Instruction                                     |

| 79~86                | <b>D</b> o <b>~ D</b> 7     | Tri-state bilateral Data Bus. The data transmission between 8- or 16-bit MPU and                                                                                                                         |

|                      |                             | NJU6572A is executed by this Bus.                                                                                                                                                                        |

| 89                   | FR                          | Alternating signal for LCD Driving output or input terminal.  Output or input is determined by master or slave mode which selected By M/S terminal.  M/S Master Slave  FR Output Input                   |

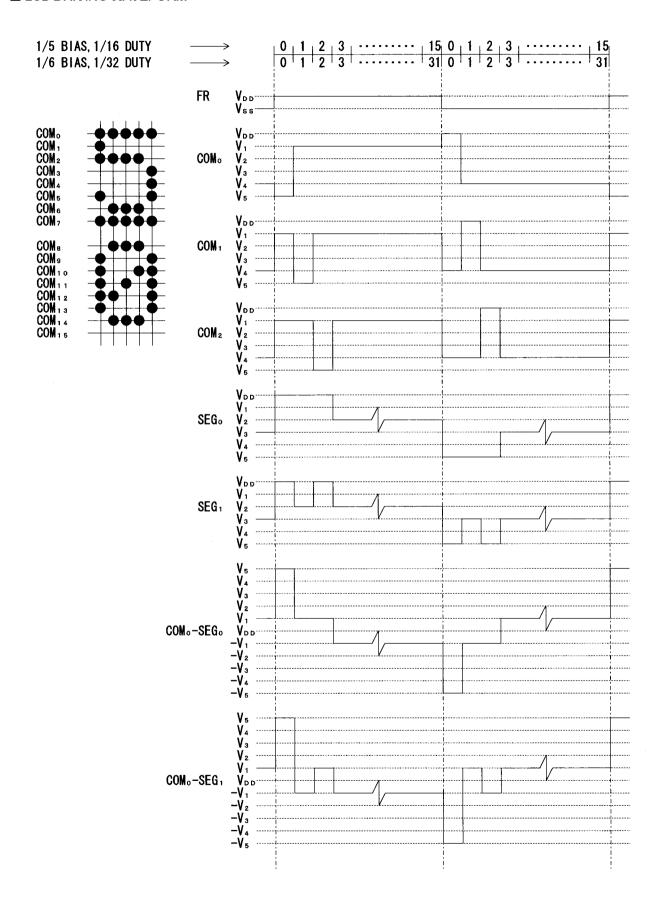

| 96~100               | COMo ~COM4<br>(COM31~COM27) | Common output terminal. One output level out of Vod, V1, V4, V5 is Selected by combination of FR and data of common counter.                                                                             |

| 1~11                 | COM5 ~ COM 1 5              | FR H L                                                                                                                                                                                                   |

|                      | (COM26~COM16)               | Data H L H L                                                                                                                                                                                             |

|                      | (Note)                      | Output V5 V1 VDD V4                                                                                                                                                                                      |

| 72~12                | SEGo ~SEGeo                 | Segment output terminal. One output level out of Vod, V2, V3, V5 is Selected by combination of FR and data of Display RAM.                                                                               |

|                      |                             | FR H L                                                                                                                                                                                                   |

|                      |                             | Data H L H L                                                                                                                                                                                             |

|                      | }                           | Output V <sub>DD</sub> V <sub>2</sub> V <sub>5</sub> V <sub>3</sub>                                                                                                                                      |

| 88                   | RST                         | Reset and Interface type select terminal. The reset operation is performed by rise or fall edge of this signal. The input level after initialization selects the interface type of 68 Or 80 type of MPU. |

| i                    | 1                           |                                                                                                                                                                                                          |

| 1                    |                             | MPU Edge Input Level after Initialization                                                                                                                                                                |

|                      | :                           | MPU Edge Input Level after Initialization 68 Type Rise H                                                                                                                                                 |

|                      |                             |                                                                                                                                                                                                          |

| 93                   | M/S<br>(Note)               | 68 Type Rise H 80 Type Fall L  Master or Slave operation selecting terminal. Connect to VDD or Vss. M/S=VDD: Master, M/S=Vss: Slave                                                                      |

| 93                   | · ·                         | Master or Slave operation selecting terminal. Connect to VDD or Vss.  M/S=VDD: Master, M/S=Vss: Slave The function of FR, COMo~COM15, OSC1, and OSC2 is changed by M/S.                                  |

| 93                   | · ·                         | Master or Slave operation selecting terminal. Connect to VDD or Vss.  M/S=VDD: Master, M/S=Vss: Slave The function of FR, COMo~COM15, OSC1, and OSC2 is changed by M/S.  N/S FR Common Output OSC1 OSC2  |

| 93                   | · ·                         | Master or Slave operation selecting terminal. Connect to VDD or Vss.  M/S=VDD: Master, M/S=Vss: Slave The function of FR, COMo~COM15, OSC1, and OSC2 is changed by M/S.                                  |

(Note) The common scanning order of slave LSI is inverted against the master LSI.

## ■ Functional Discription

## (1) Description for each blocks

#### (1-1) Busy Flag (BF)

When the internal circuits are in the operation mode, the busy flag(BF) is "1", and any instruction except the status read are inhibited.

The busy flag is output at D<sub>7</sub> terminal when status read instruction is executed.

If enough cycle time over than toyc is kept, no need to check the busy flag.

## (1-2) Display Start Line Register

The Display Start Line Register is a pointer register which indicate the address in the Display Data RAM corresponded with COM,o (normally it display the top line in the LCD Panel).

This register can use for scroll the screen, change the display page and so on.

The Display Start Line instruction set the display start address of the Display Data RAM represented in 5-bit to this register.

#### (1-3) Line Counter

The Display Start Address stored in the Display Start Line Register is set to the Line Counter when the FR signal out from the NJU6572A is changing.

The Line Counter count up by synchronizing common signal out from NJU6572A and generate the line address which addressing the read out line of Display Data RAM.

## (1-4) Column Address Counter

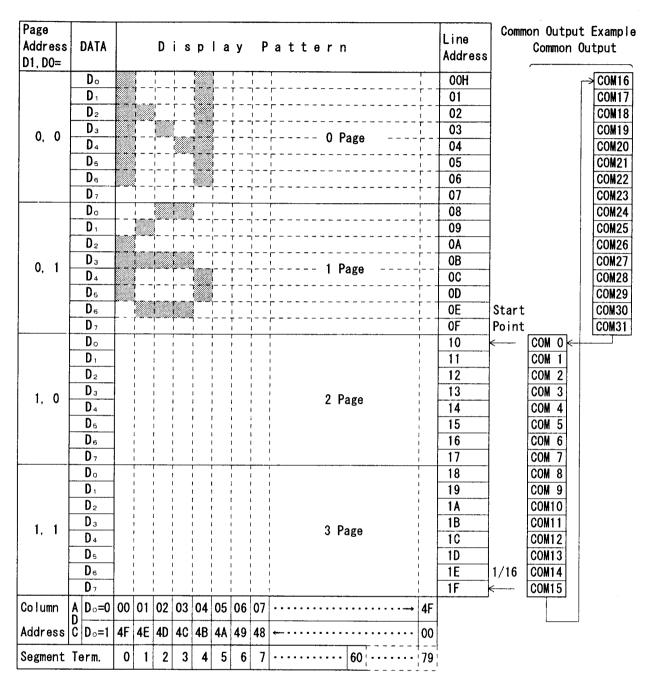

The column address counter is 7-bit presettable counter which addressing the column address as shown as Fig. 1.

This counter increments "1" up to 50H when the Display Data Read/Write instruction is executed. The count up is stop at 50H (over 50H is non existing address) automatically by the count lock function.

Furthermore, this counter is independent with the Page Register.

#### (1-5) Page Register

This register gives page address of Display Data RAM as shown Fig. 1.

When the MPU access the data by changing the page, the page address set instruction is required.

#### (1-6) Display Data RAM

Display Data Ram consist of 2,560 bits stores the bit image display data (each bit correspond to the each pixel so called bit map method). This RAM and MPU are operating independently, therefore, there is no influence by the unsynchronize rewriting.

The each bit in the Display Data RAM correspond to the each dot of the LCD panel.

The relation between column address and segment output can inverse by the Address Inverse Instruction ADC as shown Fig. 1.

## (1-7) Timing Generator

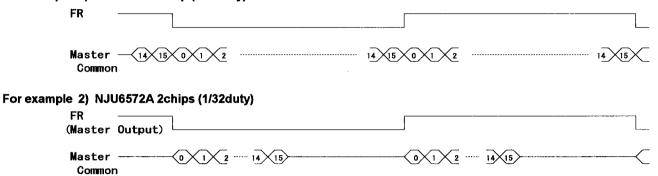

This Generator generates the common timing and frame signal for 1/16 and 1/32 duty selecting by Duty Select Instruction from the master clock.

In the case of the 1/32 duty, 2 chip of master and slave chip should be combined, and both of common are synchronized by the common multi-chip method. (Refer the figure shown below)

## For example 1) NJU6572A 1chip (1/16duty)

16 17 18 ---- 30 31

## (1-8) Display Data Latch

Slave

Common

Display Data Latch stores 80-bit of one line display data for each common cycle which read out from the Display Data RAM temporary and transfer this data to the LCD Driver.

The Display On/Off and Static Drive On/Off controls the latched data only, therefore, the data in the Display Data RAM is no change and keep on remaining.

## (1-9) LCD Driving Circuits

This Driver is consists of 80-multiplexer which output the 4-level of LCD driving voltage.

The output waveform is determined by the combination of the data in the Display Data Latch, Common Timing Generator and FR signal.

#### (1-10) Display Timing Generator

This Generator generates the timing signal for the display system by combination of the master clock and Frame Driving Signal FR. The Frame Driving Signal FR has a function to generate the 2 frame alternative driving method waveform for the LCD panel, and synchronizing the line counter and common timing generator to the master LSI. Therefore, the FR signal must be 50% duty ratio clock signal which synchronized with the frame signal.

Fig. 1. Correspondence with Display Data RAM and address (For example the display start line is 10th and 1/32 duty)

#### (1-11) Reset Circuits

The NJU6572A performs following initialization by detecting the rising or falling edge of the RST input after the power turns on.

#### Initialization

- 1, Display Off

- 2, Set the 1st line to the Display Start Register

- 3. Static Drive Off

- 4. Set the address "0" to the Column Address Counter

- 5, Set the page "3" to the Page Address Register

- 6, Select the 1/32 duty

- 7, Select the ADC : Counterclockwise output

( ADC instruction D0 = "0", ADC status flag "1")

- 8, Read Modify Write Mode Off

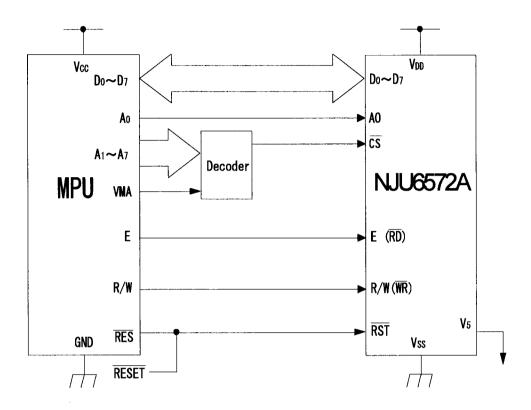

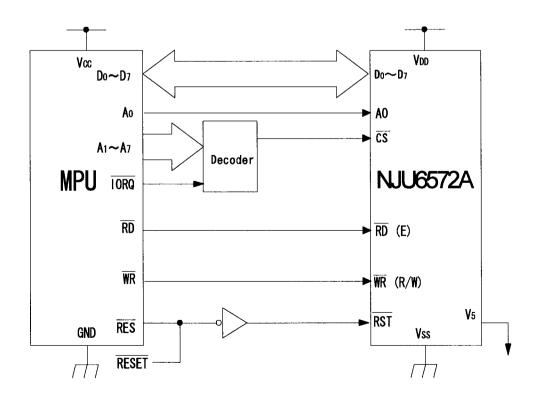

The RST terminal input level is used to select the interface of 80 or 68 type MPU as shown in Table. 2. Therefore, the "H" level input through the inverter is required when connecting the 80 type MPU, and "L" level input is required when connecting the 68 type MPU as shown in application circuits 1.

The RST terminal must be connect to the Reset Terminal of MPU and reset at same time with it.

The dead-lock may occur if the no initialization by the RST terminal when the power terns on.

By the RESET instruction, the initialization of 2 and 5 mentioned above are executed.

#### (2) Instruction

The NJU6572A distinguish the signal on the data bus by combination of A0 and R/W(RD,WR). Normally, the busy check is not required as the NJU6572A is operating so first because of the decode of the instruction and execution are performs only depend on the internal timing which not depend on the external clock. The Table, 1 shows the instruction codes of the NJU6572A.

Table 1. Instruction Code

| Instruction                     |    |    | 1  | C                     | 0 0            | d e       |                       |                 |               |     |            | Descript                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ion                               |  |  |

|---------------------------------|----|----|----|-----------------------|----------------|-----------|-----------------------|-----------------|---------------|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

|                                 | A0 | RD | WR | <b>D</b> <sub>7</sub> | D <sub>6</sub> | Dъ        | D <sub>4</sub>        | Dз              | D2            | D,  | Do         | 20001 (PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |  |  |

| Display<br>On / Off             | 0  | 1  | 0  | 1                     | 0              | 1         | 0                     | 1               | 1             | 1   | 0/1        | Whole Display On/Off.<br>1:On, 0:Off(Power Save mode<br>if the static Drive On)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |  |  |

| Display<br>Start Line           | 0  | 1  | 0  | 1                     | 1              | 1         | Dis                   | splay           | Start<br>1~31 |     | ess        | Determine the Display Line correspond to the $\text{COM}_{\circ}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |  |  |

| Page<br>Address Set             | 0  | 1  | 0  | 1                     | 0              | 1         | 1                     | 1               | 0             |     | ige<br>~3) | Set the Page of Disp. Data RAM to the Page Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |  |  |

| Column<br>Address Set           | 0  | 1  | 0  | 0                     |                | C         |                       | n Addr<br>(0∼79 |               |     |            | Set the Column Address of<br>Display Data RAM to the<br>Column Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |  |  |

| Status Read                     | 0  | 0  | 1  | B<br>U<br>S<br>Y      | A<br>D<br>C    | ON<br>OFF | R<br>E<br>S<br>E<br>T | 0               | 0             | 0   | 0          | Read the status. BUSY 1:Working 0:Ready ADC 1:Clockwise Output 0:Counterclockwise ON/OFF1:Disp Off 0:Disp O RESET 1:Reset 0:Normal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |  |  |

| Write<br>Display Data           | 1  | 1  | 0  |                       |                |           | Write                 | e Data          | 1             |     |            | Write the data to the Display Data RAM.  Access the predeter—mined add—ress of the Display Dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |  |  |

| Read<br>Display Data            | 1  | 0  | 1  |                       |                |           | Read                  | Data            |               |     |            | Read the data from the Display Data RAM.  RAM. |                                   |  |  |

| ADC Select                      | 0  | 1  | 0  | 1                     | 0              | 1         | 0                     | 0               | 0             | 0   | 0/1        | Determine the<br>counterclockwi<br>of the Display<br>0:Clockwise<br>1:Counterclo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | se reading<br>Data RAM.           |  |  |

| Static Drive<br>On / Off        | 0  | 1  | 0  | 1                     | 0              | 1         | 0                     | 0               | 1             | 0   | 0/1        | Select the Dyr<br>Static Driving<br>1:Static Dr<br>(Powe<br>0:Dynamic D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | g.<br>Tiving<br>er Saving)        |  |  |

| Duty Ratio<br>Select            | 0  | 1  | 0  | 1                     | 0              | 1         | 0                     | 1               | 0             | 0   | 0/1        | Select the dut<br>1:1/32 Duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y ratio.<br>0:1/16 Dut            |  |  |

| Read Modify<br>Write            | 0  | 1  | 0  | 1                     | 1              | 1         | 0                     | 0               | 0             | 0   | 0          | Increment the<br>ress register<br>but no-change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | when writing                      |  |  |

| End                             | 0  | 1  | 0  | 1                     | 1              | 1         | 0                     | 1               | 1             | 1   | 0          | Release from t<br>Modify Write N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |  |  |

| Reset                           | 0  | 1  | 0  | 1                     | 1              | 1         | 0                     | 0               | 0             | 1   | 0          | Set the Displa<br>Register to 1s<br>Add. Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | st line, Page                     |  |  |

| Power Save<br>(Dual<br>Command) | 0  | 1  | 0  | 1                     | 0              | 1         | 0                     | 0               | 1             | 1 0 | 0          | Set the power<br>selecting Disp<br>Static Driving<br>(The order is<br>even if it is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | olay Off and<br>g On.<br>possible |  |  |

## (3) Explanation of Instruction Code.

#### (a) Display On/Off

This instruction executes whole display On/Off no relation with the data in the Display Data RAM and internal conditions.

|      | AO | RD | R/W<br>WR | D <sub>7</sub> | D <sub>6</sub> | D۶ | D₄ | Dз | Ds | D <sub>1</sub> | Do |

|------|----|----|-----------|----------------|----------------|----|----|----|----|----------------|----|

| Code | 0  | 1  | 0         | 1              | 0              | 1  | 0  | 1  | 1  | 1              | D  |

D 0 : Display Off 1 : Display On

When the static driving mode is selected (static drive On) in display Off status, the internal circuits put on the power save mode.

## (b) Display Start Line

This instruction set the line address as shown Fig. 1. The selected line in the Display Data RAM correspond to the COMo which display at the top of LCD panel.

The display area is set automatically from the selected line to the line which increased the number of duty ratio. Therefore, the smooth scroll for vertical direction by changing the start line address one by one or page switching are available by this instruction.

|      |    |                 | R/W |                  |             |    |            |    |       |                |             |

|------|----|-----------------|-----|------------------|-------------|----|------------|----|-------|----------------|-------------|

|      | AO | $\overline{RD}$ | WR  | $\mathbf{D}_{7}$ | $D_{\rm e}$ | Dε | $D_4$      | Dз | $D_2$ | $\mathbf{D}_1$ | $D_{\circ}$ |

| Code | 0  | 1               | 0   | 1                | 1           | 0  | <b>A</b> 4 | Аз |       | <b>A</b> 1     | ۸o          |

| <b>A</b> 4 | Аз | Å <sub>2</sub> | <b>A</b> <sub>1</sub> | ۸o | Line Address |

|------------|----|----------------|-----------------------|----|--------------|

| 0          | 0  | 0              | 0                     | 0  | 0            |

| 0          | 0  | 0              | 0                     | 1  | 1            |

|            |    |                |                       |    |              |

| 1          | 1  | 1              | 1                     | 0  | 1E           |

| 1          | 1  | 1              | 1                     | 1  | 1F           |

## (c) Page Address Set

When MPU access the Display Data RAM, the page address corresponded to the row address must be selected. The access in the Display Data RAM is available by setting the page and column address. (Refer the Fig. 1.) The display is no change when the page address is changed.

|      |    |    | R/W |                |    |    |    |    |    |                |    |

|------|----|----|-----|----------------|----|----|----|----|----|----------------|----|

|      | AO | RD | WR  | D <sub>7</sub> | Dв | DБ | D₄ | Dз | D₂ | Dι             | Do |

| Code | 0  | 1  | 0   | 1              | 0  | 1  | 1  | 1  | 0  | A <sub>1</sub> | A٥ |

| A 1 | Ao | Page |

|-----|----|------|

| 0   | 0  | 0    |

| 0   | 1  | 1    |

| 1   | 0  | 2    |

| 1   | 1  | 3    |

## (d) Column Address Set

This instruction set the column address in the Display Data RAM. (See Fig.1.)

When the MPU access the Display Data RAM continuously, the column address increase "1" automatically, therefore, the MPU can access the data only without address setting.

The increment of the column address is stopped by the address of 50H automatically, but the page address is no change even if the column address increase to 50H and stop.

|      |    |    | R/W |            |    |    |                       |    |                |                       |    |

|------|----|----|-----|------------|----|----|-----------------------|----|----------------|-----------------------|----|

|      | A0 | RD | WR  | <b>D</b> 7 | Dе | Dб | <b>D</b> <sub>4</sub> | Dз | $D_2$          | <b>D</b> <sub>1</sub> | Do |

| Code | 0  | 1  | 0   | 0          | Ae | As | <b>A</b> 4            | Аз | A <sub>2</sub> | <b>A</b> 1            | Αo |

| A <sub>6</sub> | A <sub>5</sub> | <b>A</b> <sub>4</sub> | Аз | A <sub>2</sub> | <b>A</b> 1 | Ao | Colum Add. |

|----------------|----------------|-----------------------|----|----------------|------------|----|------------|

| 0              | 0              | 0                     | 0  | 0              | 0          | 0  | 0          |

| 0              | 0              | 0                     | 0  | 0              | 0          | 1  | 1          |

|                |                |                       |    |                |            |    |            |

| 1              | 0              | 0                     | 1  | 1              | 1          | 0  | 4E         |

| 1              | 0              | 0                     | 1  | 1              | 1          | 1  | 4F         |

## (e) Status Read

This instruction read out the internal status.

|      |    |    | R/W |                       |     |        |       |    |       |    |             |

|------|----|----|-----|-----------------------|-----|--------|-------|----|-------|----|-------------|

|      | AO | RD | WR  | <b>D</b> <sub>7</sub> | Dе  | Dε     |       | Дз | $D_2$ | D٦ | $D_{\rm o}$ |

| Code | 0  | 0  | 1   | BUSY                  | ADC | ON/OFF | RESET | 0  | 0     | 0  | 0           |

BUSY: BUSY=1 indicate the operating or the Reset cycle.

The instruction can be input after the BUSY status change to "0".

ADC : Indicate the output correspondence of column(segment) address and segment driver.

- 0 :Counterclockwise Output(Inverse) Column Address 79-n ←→ Segment Driver n

- 1 :Clockwise Output (Normal) Column Address n ←→ Segment Driver n

- ON/OFF: Indicate the whole display On/Off status.

0: Whole Display "On"

1: Whole Display "Off"

(Note) The data "0=On" and "1=Off" of Display On/Off status read out is inverted with the Display On/Off instruction data of "1=On" and "0=Off".

RESET: Indicate the initialization period by RST signal or reset instruction.

0:

1: Initialization Period

## (f) Display Data Write

This instruction write the 8-bit data on the data bus into the Display Data RAM.

The column(segment) address increase "1" automatically when writing, therefore, the MPU can write the 8-bit data into the Display Data RAM without address setting.

|      |    |                 | R/W |            |       |    |                       |    |       |                       |             |  |

|------|----|-----------------|-----|------------|-------|----|-----------------------|----|-------|-----------------------|-------------|--|

|      | AO | $\overline{RD}$ | WR  | <b>D</b> 7 | $D_e$ | Dь | <b>D</b> <sub>4</sub> | Dз | $D_2$ | <b>D</b> <sub>1</sub> | $D_{\circ}$ |  |

| Code | 1  | 1               | 0   |            |       | ₩r | ite                   | Da | ta    |                       |             |  |

## (g) Display Data Read

This instruction read out the 8-bit data from Display Data RAM which addressed by the column and page address. In case of the Read Modify Write Mode is Off, the column address increase "1" automatically after each read out, therefore, the MPU can read out the 8-bit data from the Display Data RAM continuously without address setting.

One time of dummy read must be required after column address set as explain in (4-3).

|      |    |    | R/W |            |    |    |                       |     |       |            |                  |

|------|----|----|-----|------------|----|----|-----------------------|-----|-------|------------|------------------|

|      | A0 | RD | WR  | <b>D</b> 7 | Dе | Dб | <b>D</b> <sub>4</sub> | Dз  | $D_2$ | <b>D</b> 1 | $D_{\mathrm{o}}$ |

| Code | 1  | 0  | 1   |            |    | R  | e a d                 | Dat | a     |            |                  |

## (h) ADC Select

This instruction set the correspondence of column address in the Display Data RAM and segment driver output. (See Fig. 1.) Therefore, the order of segment output can be changed by the software, and no restriction of the LSI placement against the LCD panel.

|      |    |                 | R/W |            |    |       |    |    |       |       |             |  |

|------|----|-----------------|-----|------------|----|-------|----|----|-------|-------|-------------|--|

|      | AO | $\overline{RD}$ | WR  | <b>D</b> 7 | Dε | $D_5$ | D₄ | Dз | $D_2$ | $D_1$ | $D_{\rm o}$ |  |

| Code | 0  | 1               | 0   | 1          | 0  | 1     | 0  | 0  | 0     | 0     | D           |  |

0 :Clockwise Output

(Inverse)

1 : CounterClockwise Output (Normal)

#### (i) Static Drive On/Of

This instruction executes the all common output terns on and whole display on obligatory.

|      |    |    | R/W |     |    |    |    |    |       |    |    |

|------|----|----|-----|-----|----|----|----|----|-------|----|----|

|      | A0 | RD | WR  | D 7 | Dб | Dε | D₄ | Dз | $D_2$ | D₁ | Do |

| Code | 0  | 1  | 0   | 1   | 0  | 1  | 0  | 0  | 1     | 0  | D  |

O : Static Drive Off (Normal Operation)

1 : Static Drive On

(Whole Display Turns On)

When the Display Off mode is selected (Display Off) in Static Drive On status, the internal circuits put on the power save mode.

## (i) Duty Select

This instruction set the LCD driving duty ratio.

|      |    |    | R/W |            |         |         |       |    |                |                |                  |

|------|----|----|-----|------------|---------|---------|-------|----|----------------|----------------|------------------|

|      | AO | RD | WR  | <b>D</b> 7 | $D^{e}$ | $D_{5}$ | $D_4$ | Dз | $\mathbf{D}_2$ | D <sub>1</sub> | $D_{\mathrm{o}}$ |

| Code | 0  | 1  | 0   | 1          | 0       | 1       | 0     | 1  | 0              | 0              | D                |

0 :1/16 duty

1:1/32 duty

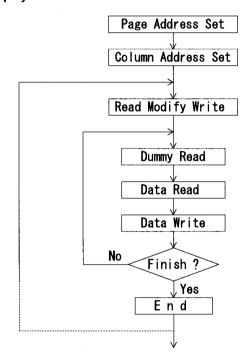

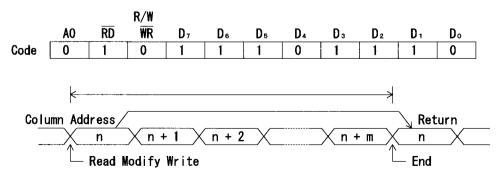

#### (k) Read Modify Write

After this instruction is executed, the column address increase "1" automatically when Display Data Write Instruction execution, but it is not changed when the Display Data Read Instruction execution.

This status continues during End instruction execution. When the End instruction is entered the column address back to the address where Read Modify Write instruction entering.

By this function, the load of MPU for example cyclic data writing operation like as cursor blink etc., can be reduced.

|      |    |    | R/W |       |       |    |    |    |       |       |         |   |

|------|----|----|-----|-------|-------|----|----|----|-------|-------|---------|---|

|      | AO | RD | WR  | $D_7$ | $D^e$ | D۶ | D₄ | Dз | $D_2$ | $D_1$ | $D_{o}$ |   |

| Code | 0  | 1  | 0   | 1     | 1     | 1  | 0  | 0  | 0     | 0     | 0       | ] |

Note) During the Read Modify Write mode, any instruction except Column Address Set can be executed.

## (I) Sequence of cursor display

## (m) End

This instruction release the Read Modify Write mode and the column address back to the address where the read modify write mode setting.

## (n) Reset

This instruction executes the following initialization.

#### Initialization

- 1, Set the 1st line in the Display Start Line Register.

- 2, Set the page 3 in the Page Register.

In this time, there are no influence to the Display Data RAM.

|      |    |    | R/W |    |                |    |    |    |       |       |             |

|------|----|----|-----|----|----------------|----|----|----|-------|-------|-------------|

|      | AO | RD | WR  | D٦ | D <sub>6</sub> | Ds | D₄ | Dз | $D_2$ | $D_1$ | $D_{\rm o}$ |

| Code | 0  | 1  | 0   | 1  | 1              | 1  | 0  | 0  | 0     | 1     | 0           |

The reset signal input to the RST terminal must be required for the initialization when the power terns on.

(Note) The initialization when the power turns on can not be executed by Reset instruction.

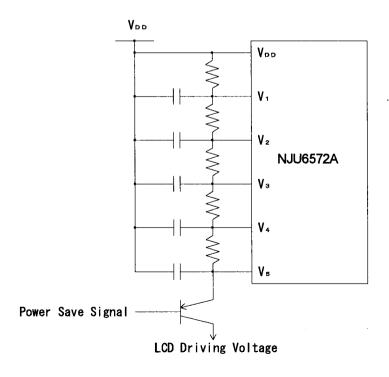

#### (o) Power Save(Dual Command)

When both of Display Off and Static Drive On are executed, the internal circuits put on the power save mode and the current consumption is reduced as same as stand by current.

The internal status in this mode are as follows;

- 1, Stop the LCD driving. Segment and Common drivers output VDD level.

- 2, Stop the oscillation or inhibit the external clock input. Then the terminal OSC<sub>2</sub> becomes floating status.

- 3, Keeping the display data and operating mode.

The power save mode is released by Display on or static drive off instruction.

To reduce the total power consumption, the current flow on the bleeder resistance must be cut by the transistor etc. during the power save mode as shown below.

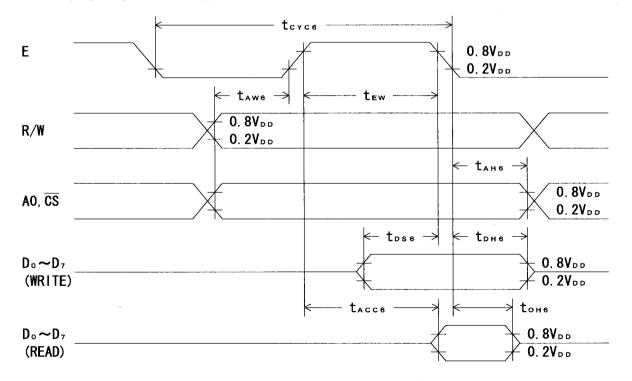

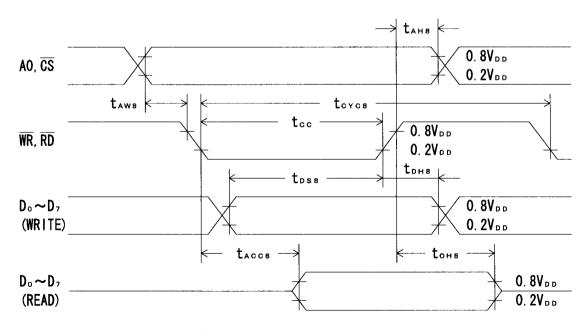

#### (4) MPU Interface

(4-1) 68 or 80 type MPU interface selection.

The NJU6572A can interface both of 68 or 80 type MPU bus directly by setting the RST level after reset instruction entered as shown Table. 2.

The data transfer is executed between D0 to D7 of NJU6572A and the MPU data bus.

Table, 2.

| Level of RST | Type of MPU | A0 | E  | R/W | Do~D7 |

|--------------|-------------|----|----|-----|-------|

| ″H″          | 68 type     | 1  | 1  | 1   | 1     |

| "L"          | 80 type     | 1  | RD | WR  | 1     |

## (4-2) Discrimination of the data bus signal.

The NJU6572A discriminates the data bus signal by combination of A0, E(RD), and R/W(WR) signals as shown Table. 3.

Table, 3.

| Common | 68 type | 80 t | :уре | Function                      |

|--------|---------|------|------|-------------------------------|

| AO     | R/W     | RD   | WR   | Function                      |

| 1      | 1       | 0    | 1    | Display Data Read out         |

| 1      | 0       | 1    | 0    | Display Data Write            |

| 0      | 1       | 0    | 1    | Status Read                   |

| 0      | 0       | 1    | 0    | Command Input to the Register |

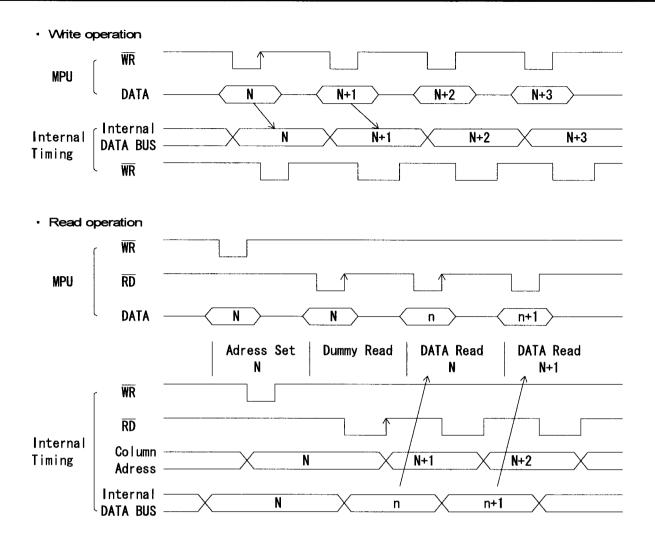

## (4-3) Access to the Display Data RAM and Internal Register.

The NJU6572A is operating as one of Pipe-line processor by the bus-holder connecting to the internal data bus to adjust the operation frequency between MPU and the Display Data RAM or Internal Register.

For example, when the MPU write the data into the Display Data RAM, the data is held in the bus-holder at once then write into the Display Data RAM by next data write cycle.

Therefore high speed data transmission between MPU and NJU6572A is available because of the limitation of access time of NJU6572A looking from MPU is just determined by the cycle time only which ignored the access time of tacc and top of Display Data RAM.

If the cycle time can not be kept in the MPU operation, NOP operation cycle must be insert which equivalent to the waiting operation.

Please note that the read out data is a address data when the read out execution just after the address setting. Therefore, one dummy read must be required after address setting or write cycle as shown in Fig. 2.

Fig.2 MPU Interface Timing

#### ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER             | SYMBOL  | RATINGS                | UNIT |

|-----------------------|---------|------------------------|------|

| Supply Voltage (1)    | V D D   | - 0.3 ~ + 7.0          | ٧    |

| Supply Voltage (2)    | V 1~V 5 | VDD - 11.0 ~ VDD + 0.3 | V    |

| Input Voltage         | V IN    | - 0.3 ~ VDD + 0.3      | ٧    |

| Operating Temperature | Topr    | - 30 ~ + 80            | °C   |

| Storage Temperature   | Tstg    | - 55 ~ + 125           | °C   |

- Note 1) If the LSI are used on condition above the absolute maximum ratings, the LSI may be destroyed. Using the LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the electric characteristics conditions will cause malfunction and poor reliability.

- Note 2) All voltage values are specified as Vss = 0 V.

- Note 3) The relation:  $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5$  must be maintained.

- Note 4) Decoupling capacitor should be connected between VDD and Vss due to the stabilized operation for the voltage converter.

#### **■ ELECTRICAL CHARACTERISTICS**

(VDD=5V±10%, Vss=0V, Ta=-20~+75°C)

| LLLOTKI       | CAL CLIAINA | CILINOII    |                  |             | (400-2      | V _ 10 /0, | V33-UV, 1a2 | 20 - 1 1 | <i>,</i> 0) |

|---------------|-------------|-------------|------------------|-------------|-------------|------------|-------------|----------|-------------|

| PARA          | AMETER      | SYMBOL      | CON              | DITIONS     | MIN.        | TYP.       | MAX.        | UNIT     | Note        |

| Operating     | Recommend   | \/nn        |                  |             | 4.5         | 5.0        | 5.5         | V        |             |

| Voltage(1)    | Available   | VDD         |                  |             | 2.4         |            | 5.5         | ·        | 5           |

|               | Recommend   | \ /-        |                  |             | VDD-10      |            | VDD-3.5     |          |             |

| Operating     | Available   | V5          |                  |             | VDD-10      |            |             | V        |             |

| Voltage(2)    | Available   | V1, V2      | \/, cp=\/pp\//   |             | VDD-0.6VLCD |            | VDD         | •        |             |

|               | Available   | V3, V4      | VLCD=VDD-V5      | 1           | V5          |            | VDD-0.4VLCD |          |             |

|               | 4           | ViHT        | ĈŜ, A0, D0~D     | 7, E, R/W   | 2.0         |            | VDD         |          |             |

| Input         | 1           | VILT        |                  | Terminals   | Vss         |            | 0.8         | v        | İ           |

| Voltage       | 2           | VIHC        | CL, FR, M/S,     | RST         | 0.8VDD      |            | VDD         | V        |             |

|               | -           | VILC        | 1                | Terminals   | Vss         |            | 0.2VDD      |          |             |

|               |             | Vонт        | D0~D7            | lo+=-3.0mA  | 2.4         |            |             |          |             |

|               |             | VOLT        | Terminals        | IOL= 3.0mA  |             |            | 0.4         |          |             |

| Output        |             | Vohc1       | ED Townsin of    | lo+=-2.0mA  | 2.4         |            |             | v        |             |

| Voltage       | 1           | Volc1       | FR Terminal      | IOL= 2.0mA  |             |            | 0.4         | \ \ \    |             |

|               |             | VOHC2       | Cl. Towningl     | loH=-120uA  | 0.8VDD      |            |             |          |             |

|               | 2           | VOLC2       | CL Terminal      | IOL= 120uA  |             |            | 0.2VDD      |          |             |

| مرامم المرسوا | O           | <b>I</b> LI | A0, E, RW, C     | S, CL, RST  | -1.0        |            | 1.0         |          |             |

| Input Leeka   | ge Current  | ILO         | Do~D7, FR Te     | rminals     | -3.0        |            | 3.0         | uA       | 6           |

| Driver On r   | :           | Bou         |                  | V5=VDD-5.0V |             | 5.0        | 7.5         | 10       | 7           |

| Driver On-re  | esistance   | RON         | Term.<br>Ta=25°C | V5=VDD-3.5V |             | 10.0       | 50.0        | kΩ       | '           |

| Stand-by C    | urrent      | IDDQ        | M/S=Vss, CS      | =CL=VDD     |             | 0.05       | 1.0         | uΑ       |             |

| Operating (   | D. uma sub  | IDD1        | Display V5=0\    | /, fcL=2kHz |             | 9.5        | 15.0        |          |             |

| Operating (   | Jurreni     | IDD2        | Accessing, tcy   | /c=200kHz   |             | 300        | 500         | uΑ       | 8           |

| External Clo  | ock         | fCL         |                  |             |             | 2.0        |             | kHz      |             |

| Reset Time    | 1           | tR          | RST Terminal     |             | 1.0         |            | 1000        | us       |             |